TC03 TAPE COUPLER (TS11 COMPATIBLE) TECHNICAL MANUAL

3545 Harbor Boulevard Costa Mesa, California 92626 (714) 662-5600 TWX 910-595-2521

TC0351001 Rev A September 1985

#### WARNING

This equipment generates, uses, and can radiate radio-frequency energy, and if not installed and used in accordance with the technical manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of Federal Communications Commission (FCC) Rules, which are designed to provide reasonable protection against such interference when operating in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Copyright (C) 1985 Emulex Corporation

The information in this manual is for information purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in the manual.

Printed in U.S.A.

# TABLE OF CONTENTS

| ~    | - | - |     | 2  | - |   |

|------|---|---|-----|----|---|---|

| - 54 | ρ | e | fr. | ъ. | റ | n |

| ~    | ~ | ~ | -   | -  | ~ |   |

# Title

| ONE | GENERAL | DESCRIPTION |

|-----|---------|-------------|

|     |         | s.          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-1                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 1.1.1 RELATED DOCUMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-2                                                                |

| 1.1.2 DEFINITIONS OF TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| 1.2 SUBSYSTEM OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |

| 1.3 PHYSICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-5                                                                |

| 1.4 SUBSYSTEM MODELS AND OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

| 1.4.1 SUBSYSTEM OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-6                                                                |

| 1.5 FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-9                                                                |

| 1.5.1 MICROPROCESSOR ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-9                                                                |

| 1.5.2 CONFIGURATION FLEXIBILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |

| 1.5.3 SELF-TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |

| 1.5.4 BUFFERING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-9                                                                |

| 1.5.5 DATA TRANSFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

| 1.5.6 BOOTSTRAP OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |

| 1.6 COMPATIBILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

| 1.6.1 MEDIA COMPATIBILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

| 1.6.2 TAPE TRANSPORTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |

| 1.6.3 DIAGNOSTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

| 1.6.4 OPERATING SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |

| 1.7 HARDWARE COMPATIBILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-11                                                               |

| TWO SPECIFICATIONS 2.1 OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-1                                                                |

| 2.2 GENERAL SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-1                                                                |

| 2.2 GIADRAL DEBCIFICATIOND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-1                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |

| THREE PLANNING THE INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |

| 3.1 OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

| <b>3.1 OVERVIEW</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-1                                                                |

| 3.1 OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-1<br>3-1                                                         |

| 3.1OVERVIEW3.1.1CONFIGURATION DEFINED3.2DEC TS11 ARCHITECTURE3.3DEC TS11 SUBSYSTEM CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-1<br>3-1<br>3-2                                                  |

| 3.1OVERVIEW3.1.1CONFIGURATION DEFINED3.2DEC TS11 ARCHITECTURE3.3DEC TS11 SUBSYSTEM CONFIGURATION3.4TC03 SUBSYSTEM CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-1<br>3-1<br>3-2<br>3-2                                           |

| <pre>3.1 OVERVIEW</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-1<br>3-1<br>3-2<br>3-2<br>3-3                                    |

| <pre>3.1 OVERVIEW</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-1<br>3-1<br>3-2<br>3-2<br>3-3<br>3-4                             |

| <pre>3.1 OVERVIEW</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-1<br>3-1<br>3-2<br>3-2<br>3-3                                    |

| <pre>3.1 OVERVIEW</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-1<br>3-1<br>3-2<br>3-2<br>3-3<br>3-4                             |

| <pre>3.1 OVERVIEW</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-1<br>3-1<br>3-2<br>3-2<br>3-3<br>3-4                             |

| <pre>3.1 OVERVIEW 3.1.1 CONFIGURATION DEFINED 3.2 DEC TS11 ARCHITECTURE 3.3 DEC TS11 SUBSYSTEM CONFIGURATION 3.4 TC03 SUBSYSTEM CONFIGURATION 3.4.1 Device Numbering 3.5 OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES 3.6 PERFORMANCE CONSIDERATIONS FOUR INSTALLATION 4.1 OVERVIEW</pre>                                                                                                                                                                                                                                                                                          | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>3-5                             |

| <pre>3.1 OVERVIEW 3.1.1 CONFIGURATION DEFINED 3.2 DEC TS11 ARCHITECTURE 3.3 DEC TS11 SUBSYSTEM CONFIGURATION 3.4 TCO3 SUBSYSTEM CONFIGURATION 3.4.1 Device Numbering 3.5 OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES 3.6 PERFORMANCE CONSIDERATIONS FOUR INSTALLATION 4.1 OVERVIEW 4.1.1 SUBSYSTEM CONFIGURATIONS</pre>                                                                                                                                                                                                                                                           | 3-1<br>3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>3-5                      |

| <pre>3.1 OVERVIEW 3.1.1 CONFIGURATION DEFINED 3.2 DEC TS11 ARCHITECTURE 3.3 DEC TS11 SUBSYSTEM CONFIGURATION 3.4 TC03 SUBSYSTEM CONFIGURATION 3.4.1 Device Numbering 3.5 OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES 3.6 PERFORMANCE CONSIDERATIONS FOUR INSTALLATION 4.1 OVERVIEW</pre>                                                                                                                                                                                                                                                                                          | 3-1<br>3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-1        |

| <pre>3.1 OVERVIEW 3.1.1 CONFIGURATION DEFINED 3.2 DEC TS11 ARCHITECTURE 3.3 DEC TS11 SUBSYSTEM CONFIGURATION 3.4 TCO3 SUBSYSTEM CONFIGURATION 3.4.1 Device Numbering 3.5 OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES 3.6 PERFORMANCE CONSIDERATIONS FOUR INSTALLATION 4.1 OVERVIEW 4.1.1 SUBSYSTEM CONFIGURATIONS 4.1.2 DIP SWITCH TYPES 4.1.3 MAINTAINING FCC CLASS A COMPLIANCE</pre>                                                                                                                                                                                           | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-1<br>4-1<br>4-3 |

| <pre>3.1 OVERVIEW 3.1.1 CONFIGURATION DEFINED 3.2 DEC TS11 ARCHITECTURE 3.3 DEC TS11 SUBSYSTEM CONFIGURATION 3.4 TCO3 SUBSYSTEM CONFIGURATION 3.4.1 Device Numbering 3.5 OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES 3.6 PERFORMANCE CONSIDERATIONS 4.1 OVERVIEW 4.1.1 SUBSYSTEM CONFIGURATIONS 4.1.2 DIP SWITCH TYPES 4.1.3 MAINTAINING FCC CLASS A COMPLIANCE</pre>                                                                                                                                                                                                             | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-1<br>4-3<br>4-3 |

| <ul> <li>3.1 OVERVIEW</li> <li>3.1.1 CONFIGURATION DEFINED</li> <li>3.2 DEC TS11 ARCHITECTURE</li> <li>3.3 DEC TS11 SUBSYSTEM CONFIGURATION</li> <li>3.4 TCO3 SUBSYSTEM CONFIGURATION</li> <li>3.4.1 Device Numbering</li> <li>3.5 OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES</li> <li>3.6 PERFORMANCE CONSIDERATIONS</li> <li>FOUR INSTALLATION</li> <li>4.1 OVERVIEW</li> <li>4.1.1 SUBSYSTEM CONFIGURATIONS</li> <li>4.1.2 DIP SWITCH TYPES</li> <li>4.1.3 MAINTAINING FCC CLASS A COMPLIANCE</li> <li>4.2 INSPECTION</li> <li>4.3 TCO3 TAPE COUPLER CONFIGURATION</li> </ul> | 3-1 3-2 3-2 3-3 3-4 3-5 4-1 4-1 4-3 4-3 4-4                        |

| <pre>3.1 OVERVIEW 3.1.1 CONFIGURATION DEFINED 3.2 DEC TS11 ARCHITECTURE 3.3 DEC TS11 SUBSYSTEM CONFIGURATION 3.4 TCO3 SUBSYSTEM CONFIGURATION 3.4.1 Device Numbering 3.5 OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES 3.6 PERFORMANCE CONSIDERATIONS 4.1 OVERVIEW 4.1.1 SUBSYSTEM CONFIGURATIONS 4.1.2 DIP SWITCH TYPES 4.1.3 MAINTAINING FCC CLASS A COMPLIANCE 4.2 INSPECTION 4.3 TCO3 TAPE COUPLER CONFIGURATION 4.3.1 TCO3 TAPE COUPLER MODES</pre>                                                                                                                            | 3-1 3-2 3-2 3-3 3-4 3-5 $4-1 4-1 4-3 4-3 4-4 4-4$                  |

| <ul> <li>3.1 OVERVIEW</li> <li>3.1.1 CONFIGURATION DEFINED</li> <li>3.2 DEC TS11 ARCHITECTURE</li> <li>3.3 DEC TS11 SUBSYSTEM CONFIGURATION</li> <li>3.4 TCO3 SUBSYSTEM CONFIGURATION</li> <li>3.4.1 Device Numbering</li> <li>3.5 OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES</li> <li>3.6 PERFORMANCE CONSIDERATIONS</li> <li>FOUR INSTALLATION</li> <li>4.1 OVERVIEW</li> <li>4.1.1 SUBSYSTEM CONFIGURATIONS</li> <li>4.1.2 DIP SWITCH TYPES</li> <li>4.1.3 MAINTAINING FCC CLASS A COMPLIANCE</li> <li>4.2 INSPECTION</li> <li>4.3 TCO3 TAPE COUPLER CONFIGURATION</li> </ul> | 3-1 3-2 3-2 3-3 3-4 3-5 $4-1 4-1 4-1 4-3 4-3 4-4 4-4 4-7$          |

| 4.3.1.3 <u>Combination Mode</u>                                                                      | 4-8        |

|------------------------------------------------------------------------------------------------------|------------|

| 4.3.2 TAPE COUPLER BUS ADDRESS SELECTION                                                             | 4-8        |

| 4.3.3 INDIVIDUAL TAPE TRANSPORT ENABLING                                                             | 4-10       |

| 4.3.4 INTERRUPT VECTOR ADDRESS                                                                       | 4-10       |

| 4.3.5 OPTIONS                                                                                        | 4-12       |

| 4.3.5.1 <u>Run/Reset Option</u>                                                                      | 4-12       |

| 4.3.5.2 <u>Twenty-two-bit Addressing Option</u>                                                      | 4-12       |

| 4.3.5.3 <u>Remote Density Select</u>                                                                 | 4-12       |

|                                                                                                      | 4-13       |

|                                                                                                      | 4-13       |

|                                                                                                      | 4-14       |

|                                                                                                      | 4-14       |

| 4.3.5.7 Write Data Strobe Option                                                                     | 4-15       |

| 4.4 TC03 TAPE COUPLER INSTALLATION                                                                   | 4-15       |

| 4.4.1 CPU PREPARATION                                                                                |            |

| 4.4.2 SLOT SELECTION                                                                                 |            |

| 4.4.3 MOUNTING                                                                                       | 4-16       |

| 4.5 TAPE TRANSPORT PREPARATION                                                                       | 4-16       |

| 4.5.1 DAISY CHAIN OPERATION                                                                          |            |

| 4.5.2 STANDARD VENDOR CONFIGURATIONS                                                                 | 4-17       |

| 4.5.3 GENERAL OPERATING RESTRICTIONS                                                                 | 4-18       |

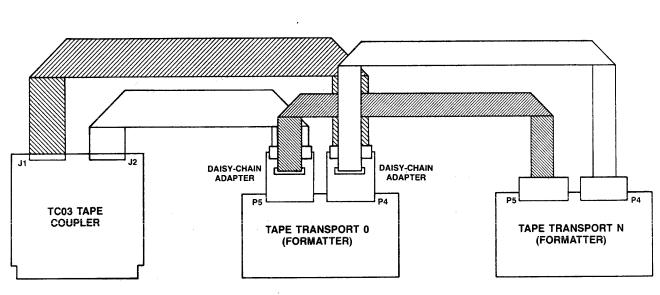

| 4.6 CABLING                                                                                          | 4-18       |

| 4.6.1 GROUNDING                                                                                      |            |

| 4.6.2 FORMATTED SUBSYSTEMS                                                                           | 4-20       |

| 4.6.2.1 Daisy-Chaining                                                                               | 4-21       |

| 4.6.3 STREAMING SUBSYSTEMS                                                                           | 4-22       |

| 4.6.3.1 <u>Daisy-Chaining</u>                                                                        |            |

| 4.6.4 COMBINATION SUBSYSTEMS                                                                         | 4-22       |

| 4.6.5 RFI SUPPRESSION                                                                                | 4-24       |

| 4.6.5.1 <u>RFI-Suppression Devices</u>                                                               | 4-24       |

| 4.6.5.2 Equipment Cabinet                                                                            | 4-24       |

| A 6 5 2 ] Come Cabinet                                                                               | 4-28       |

| 4.6.5.2.1 <u>Same Cabinet</u>                                                                        | 4-30       |

| 4.6.5.2.2 <u>Separate Cabinets</u>                                                                   | 4-30       |

|                                                                                                      |            |

| 4.7.1 SELF-TEST                                                                                      |            |

| 4.7.2 DIAGNOSTICS                                                                                    | 4-31       |

| 4.7.3 BOOTSTRAP INSTRUCTIONS                                                                         | 4-33       |

|                                                                                                      |            |

| FIVE TROUBLESHOOTING                                                                                 |            |

| 5.1 OVERVIEW                                                                                         | 5-1        |

| 5.2 SERVICE                                                                                          |            |

| 5.3 FAULT ISOLATION                                                                                  | 5-1        |

| 5.4 POWER-UP SELF-DIAGNOSTIC                                                                         | 5-2        |

| J.4 POWER-UP SELF-DIAGNOSTIC                                                                         | 5-4        |

| SIX COUPLER REGISTERS AND PROGRAMMING                                                                |            |

| 6.1 OVERVIEW                                                                                         | 6-1        |

| 6.2 COUPLER REGISTERS                                                                                | 6-1<br>6-1 |

| 6.2.1 LSI-11 BUS BASE ADDRESS REGISTER (TSBA)                                                        |            |

| 6.2.2 LSI-11 BUS DATA BUFFER (TSDB)                                                                  | 6-3        |

| 6 2 2 1 Normal Operation                                                                             | 6-3        |

| 6.2.2.1 <u>Normal Operation</u><br>6.2.2.2 <u>Data Wraparound by Using DATOB (Odd)</u>               | 6-3        |

| 6.2.2.3 Data Wraparound by Using DATOB (Odd)                                                         | 6-4<br>6-4 |

| $v \in a \in a$ , $u \in a$ , $u \in a \cup a \in a \cup a \in a \cup a \cup a \cup a \cup a \cup a$ | 6 - A      |

| 6.2.3 STATUS REGISTER (TSSR)                                                                                                                   | 6-5          |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 6.2.3.1 Bootstrap Command                                                                                                                      | 6-8          |

| 6.2.4 EXTENDED STATUS REGISTERS                                                                                                                |              |

| 6.2.4 EXTENDED STATUS REGISTERS                                                                                                                | 6-11         |

| 6.2.4.1 <u>Residual Frame Count Register (RBPCR)</u>                                                                                           | 6_11         |

| 6.2.4.2 Extended Status Register Zero (XSTO)                                                                                                   | 6-14         |

| 6.2.4.3 <u>Extended Status Register 1 (XST1)</u>                                                                                               | V-14<br>6.15 |

| 6.2.4.4 <u>Extended Status Register 2 (XST2)</u>                                                                                               | 0-15         |

| 6.2.4.5 Extended Status Register 3 (XST3)                                                                                                      | 0-15         |

| 6.3 COMMAND PACKET PROCESSING                                                                                                                  | 0-10         |

| 6.3.1 BUFFER OWNERSHIP AND CONTROL                                                                                                             | 6-16         |

| 6.3.2 BUFFER CONTROL WITH ATTENTION ENABLED                                                                                                    | 6-18         |

| 6.3.3 COMMAND PACKET/HEADER WORD                                                                                                               | 6-21         |

| 6.3.4 COMMAND PACKET EXAMPLES                                                                                                                  | 6-26         |

| 6.3.4.1 Get Status Command                                                                                                                     | 6-26         |

| 6.3.4.2 <u>Read Command</u>                                                                                                                    | 6-27         |

| 6.3.4.3 Set Characteristics Command                                                                                                            | 6-28         |

| 6.3.4.4 Write Command                                                                                                                          | 6-31         |

| 6.3.4.5 Position Command                                                                                                                       | 6-33         |

| 6.3.4.6 Format Command                                                                                                                         | 6-34         |

| 6.3.4.7 Control Command                                                                                                                        | 6-35         |

| 6348 Initialize Command                                                                                                                        | 6-37         |

| C 2 5 MESCACE DACKET HEADED WORD                                                                                                               | 6-37         |

|                                                                                                                                                |              |

| 6.3.5.1 <u>Message Packet Example</u><br>6.4 PROGRAMMING OPERATIONS<br>6.4.1 LSI-11 BUS REGISTERS<br>6.4.2 COMMAND PACKETS AND MESSAGE PACKETS | 6-39         |

| CALLET IL DUC DECICIEDC                                                                                                                        | 6-40         |

| 0.4.1 LSI-II BUD REGIDIERD                                                                                                                     | 6-40         |

| 6.4.2 COMMAND PACKETS AND MESSAGE FACKETS                                                                                                      | 6-41         |

| 6.4.3 SPECIAL CONDITIONS AND ERRORS                                                                                                            | 6-41         |

| 6.4.4 STATUS ERROR HANDLING TECHNIQUES                                                                                                         | 0 41         |

| SEVEN FUNCTIONAL DESCRIPTION                                                                                                                   |              |

| SEVEN FUNCTIONAL DESCRIPTION                                                                                                                   |              |

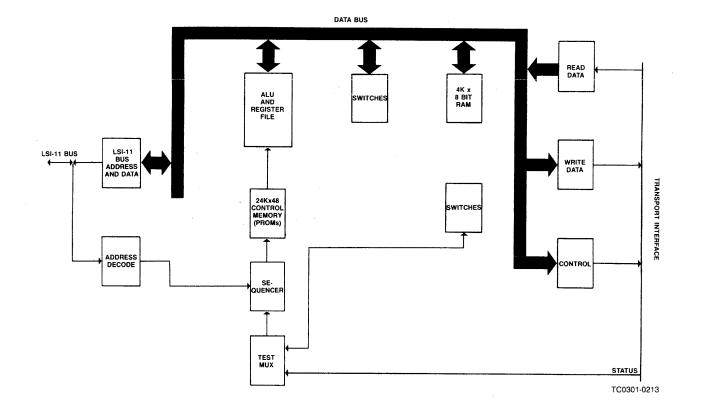

| 7.1 OVERVIEW                                                                                                                                   | 7-1          |

|                                                                                                                                                | 7-1          |

|                                                                                                                                                |              |

| 7.2.1 ORGANIZATION                                                                                                                             | •            |

| 7.2.2 RAM BUFFER                                                                                                                               |              |

| 7.2.3 DATA AND CONTROL REGISTERS                                                                                                               | 7-3          |

| 7.2.4 MICROPROCESSOR RELATIONSHIPS                                                                                                             | 7-3          |

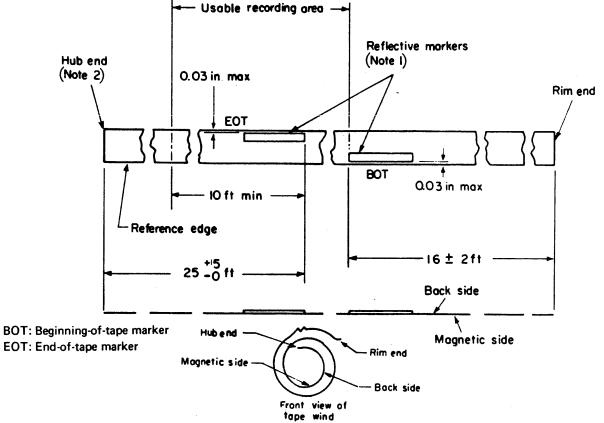

| 7.3 TAPE FORMAT                                                                                                                                | 7-3          |

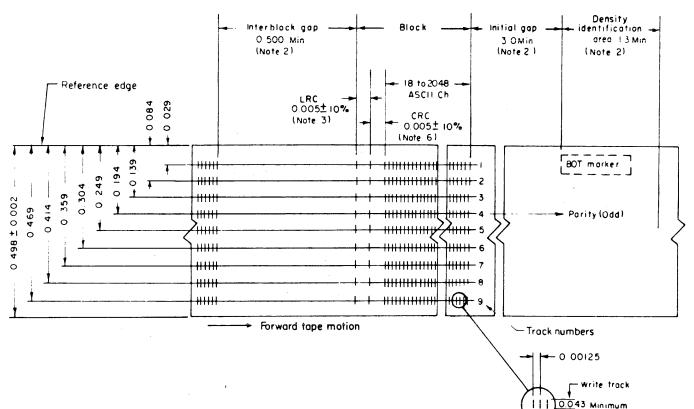

| 7.3.1 NRZI FORMAT                                                                                                                              | 7-5          |

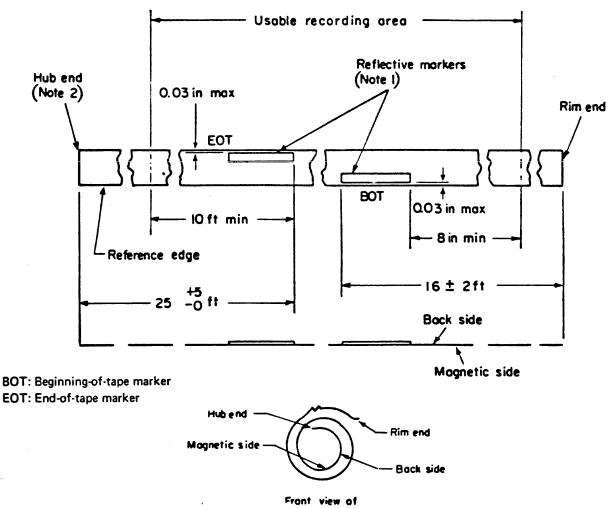

| 7.3.2 PE FORMAT                                                                                                                                | 7-5          |

| 7.3.3 GCR FORMAT                                                                                                                               | /-8          |

| EIGHT INTERFACES                                                                                                                               |              |

|                                                                                                                                                | ~ -          |

| 8.1 OVERVIEW                                                                                                                                   | 8-1          |

| 8.2 LSI-11 BUS INTERFACE                                                                                                                       | 8-1          |

| 8.2.1 INTERRUPT PRIORITY LEVEL                                                                                                                 | 8-4          |

| 8.2.2 REGISTER ADDRESS                                                                                                                         | 8-4          |

| 8.2.3 DCOK AND INIT SIGNALS                                                                                                                    | 8-4          |

| 8.2.4 NPR OPERATIONS                                                                                                                           | 8-4          |

| 8.3 TAPE TRANSPORT INTERFACE                                                                                                                   | 8-4          |

| 8.3.1 CONNECTORS AND CABLE                                                                                                                     | 8-4          |

| 8.3.2 INPUT CIRCUITS                                                                                                                           | 8-5          |

| 8.3.3 OUTPUT CIRCUITS<br>8.3.4 SIGNAL DEFINITIONS                                                                                                                                                                                                                 | 8-5                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|                                                                                                                                                                                                                                                                   |                                                           |

| 8.3.4.1 <u>Coupler to Formatter</u>                                                                                                                                                                                                                               | 8-5                                                       |

| 8.3.4.2 Formatter to Coupler                                                                                                                                                                                                                                      | 8-7                                                       |

| APPENDIX A: AUTOCONFIGURE, BASE AND VECTOR ADDRESSES                                                                                                                                                                                                              |                                                           |

| A.1 OVERVIEW<br>A.2 DETERMINING THE CSR ADDRESS FOR USE WITH                                                                                                                                                                                                      | A-1                                                       |

| AUTOCONFIGURE                                                                                                                                                                                                                                                     | A-1                                                       |

| A.3 DETERMINING THE VECTOR ADDRESS FOR USE WITH                                                                                                                                                                                                                   |                                                           |

| AUTOCONFIGURE<br>A.4 A SYSTEM CONFIGURATION EXAMPLE                                                                                                                                                                                                               | A-3<br>A-6                                                |

|                                                                                                                                                                                                                                                                   |                                                           |

| APPENDIX B: PROM REMOVAL AND REPLACEMENT                                                                                                                                                                                                                          |                                                           |

| B.1 OVERVIEW                                                                                                                                                                                                                                                      | B-1                                                       |

| B.2 LOCATION                                                                                                                                                                                                                                                      | B-1                                                       |

| B.3 REMOVAL AND REPLACEMENT                                                                                                                                                                                                                                       | B-2                                                       |

|                                                                                                                                                                                                                                                                   |                                                           |

| APPENDIX C: DRIVE CONFIGURATION                                                                                                                                                                                                                                   |                                                           |

|                                                                                                                                                                                                                                                                   |                                                           |

| C.1 OVERVIEW                                                                                                                                                                                                                                                      | C-1                                                       |

| C.1 OVERVIEW                                                                                                                                                                                                                                                      | C-1                                                       |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02                                                                                                                                                                                                       | C-1<br>C-3                                                |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891                                                                                                                                                                                     | C-1<br>C-3<br>C-9                                         |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400                                                                                                                                               | C-1<br>C-3<br>C-9<br>C-11                                 |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400<br>C.7 KENNEDY 9000F, 9100F, AND 9300F                                                                                                        | C-1<br>C-3<br>C-9<br>C-11<br>C-13                         |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400<br>C.7 KENNEDY 9000F, 9100F, AND 9300F<br>C.7.1 Switches                                                                                      | C-1<br>C-3<br>C-9<br>C-11<br>C-13<br>C-14                 |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400<br>C.7 KENNEDY 9000F, 9100F, AND 9300F<br>C.7.1 <u>Switches</u><br>C.7.2 Interface Cabling Requirements                                       | C-1<br>C-3<br>C-9<br>C-11<br>C-13<br>C-14<br>C-15         |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400<br>C.7 KENNEDY 9000F, 9100F, AND 9300F<br>C.7.1 <u>Switches</u><br>C.7.2 <u>Interface Cabling Requirements</u>                                | C-1<br>C-3<br>C-9<br>C-11<br>C-13<br>C-14<br>C-15<br>C-15 |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400<br>C.7 KENNEDY 9000F, 9100F, AND 9300F<br>C.7.1 <u>Switches</u><br>C.7.2 Interface Cabling Requirements                                       | C-1<br>C-3<br>C-9<br>C-11<br>C-13<br>C-14<br>C-15         |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400<br>C.7 KENNEDY 9000F, 9100F, AND 9300F<br>C.7.1 <u>Switches</u><br>C.7.2 <u>Interface Cabling Requirements</u><br>C.7.3 <u>Daisy-Chaining</u> | C-1<br>C-3<br>C-9<br>C-11<br>C-13<br>C-14<br>C-15<br>C-15 |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400<br>C.7 KENNEDY 9000F, 9100F, AND 9300F<br>C.7.1 <u>Switches</u><br>C.7.2 <u>Interface Cabling Requirements</u><br>C.7.3 <u>Daisy-Chaining</u> | C-1<br>C-3<br>C-9<br>C-11<br>C-13<br>C-14<br>C-15<br>C-15 |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400<br>C.7 KENNEDY 9000F, 9100F, AND 9300F<br>C.7.1 <u>Switches</u><br>C.7.2 <u>Interface Cabling Requirements</u><br>C.7.3 <u>Daisy-Chaining</u> | C-1<br>C-3<br>C-9<br>C-11<br>C-13<br>C-14<br>C-15<br>C-15 |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400<br>C.7 KENNEDY 9000F, 9100F, AND 9300F<br>C.7.1 <u>Switches</u><br>C.7.2 <u>Interface Cabling Requirements</u><br>C.7.3 <u>Daisy-Chaining</u> | C-1<br>C-3<br>C-9<br>C-11<br>C-13<br>C-14<br>C-15<br>C-15 |

| C.1 OVERVIEW<br>C.2 CDC 92181<br>C.3 CDC 92185 AND 92185-02<br>C.4 CIPHER 891<br>C.5 CIPHER 990<br>C.6 KENNEDY 9400<br>C.7 KENNEDY 9000F, 9100F, AND 9300F<br>C.7.1 <u>Switches</u><br>C.7.2 <u>Interface Cabling Requirements</u><br>C.7.3 <u>Daisy-Chaining</u> | C-1<br>C-3<br>C-9<br>C-11<br>C-13<br>C-14<br>C-15<br>C-15 |

# LIST OF FIGURES

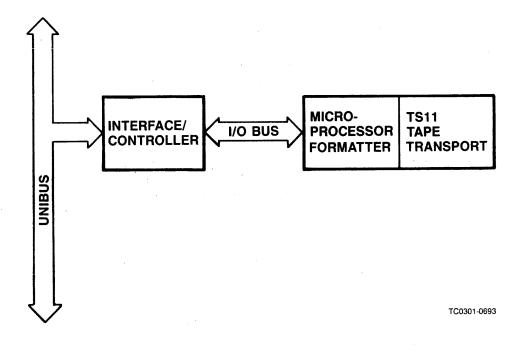

| Figure 1-1.  | TC03 Subsystem Configuration                  | 1-4  |

|--------------|-----------------------------------------------|------|

| Figure 1-2.  | TC03 Tape Coupler                             | 1-6  |

| Figure 1-3.  | Sales Order Example                           | 1-6  |

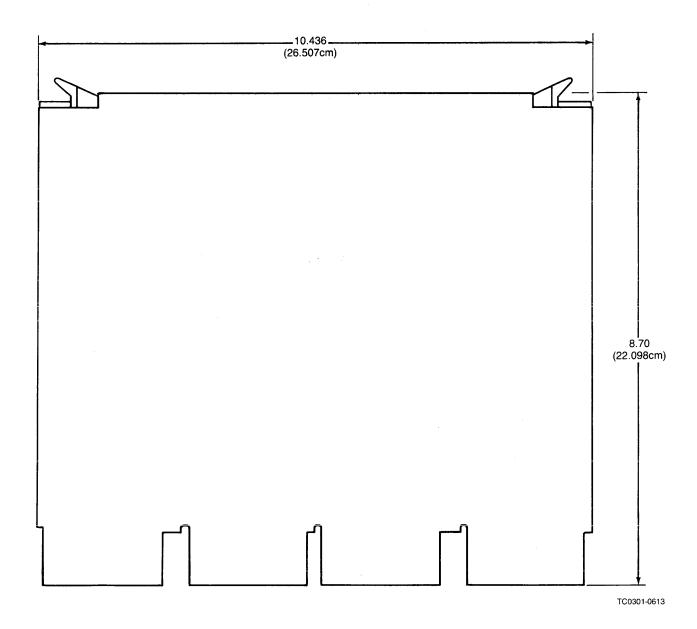

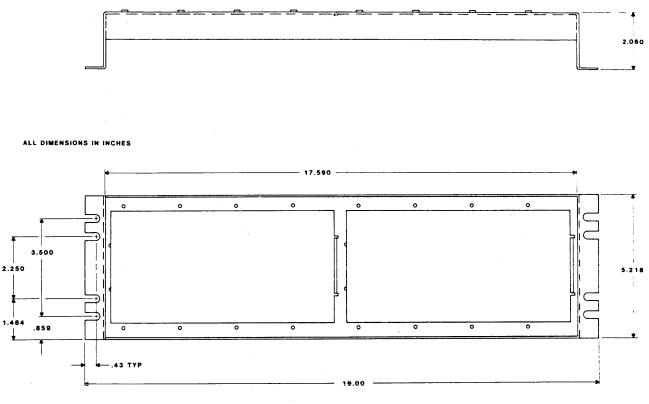

| Figure 2-1.  | TC03 Tape Coupler Dimensions                  | 2-3  |

| Figure 3-1.  | DEC TS11 Subsystem Logical and Physical       |      |

| -            | Configuration                                 | 3-2  |

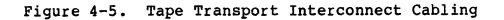

| Figure 3-2.  | TC03 Subsystem Logical and Physical           |      |

| -            | Configuration                                 | 3-3  |

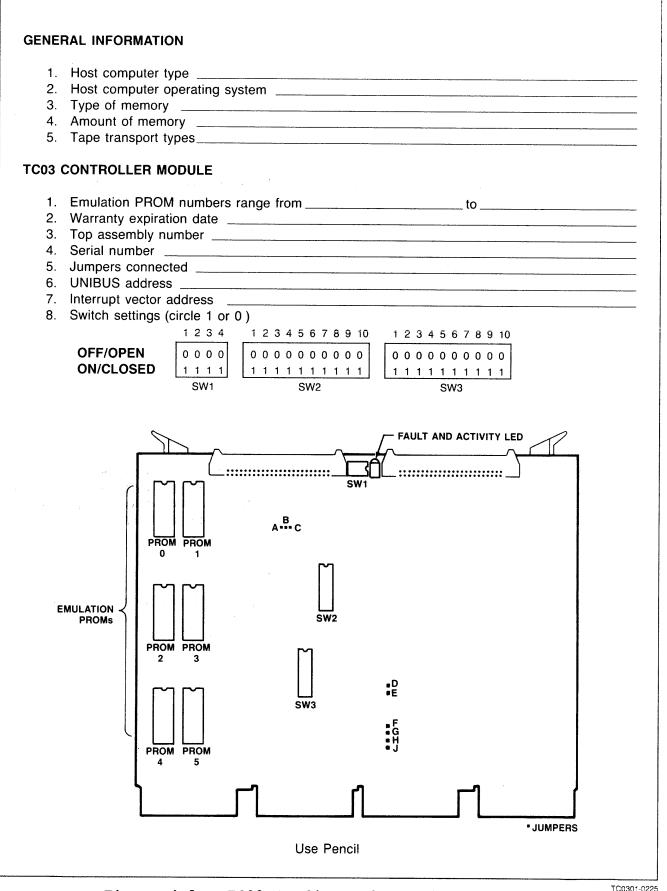

| Figure 4-1.  | TC03 Configuration Reference Sheet            | 4-2  |

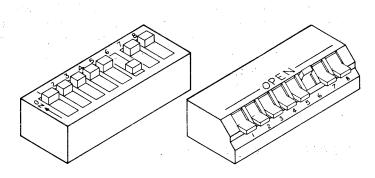

| Figure 4-2.  | Switch Setting Example                        | 4-3  |

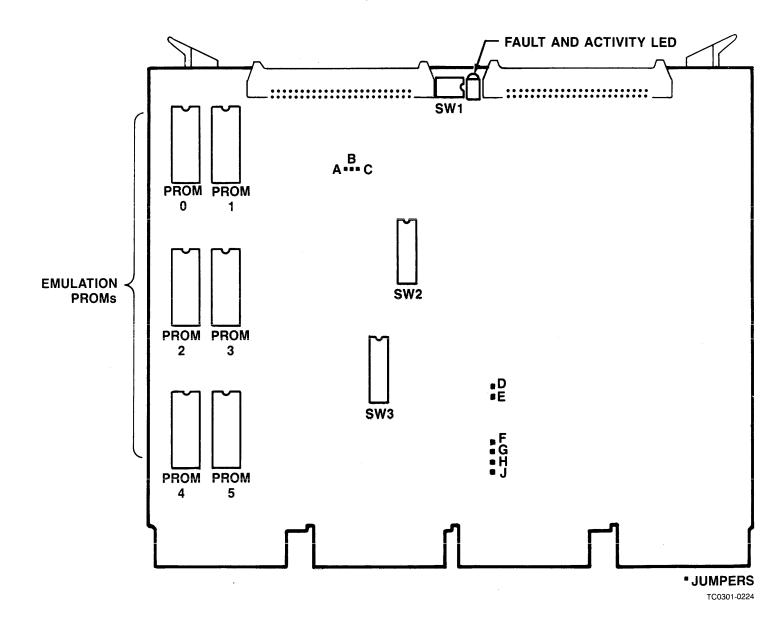

| Figure 4-3.  | TC03 Tape Coupler Component Locations         | 4-5  |

| Figure 4-4.  | Interrupt Vector Address Selection            | 4-10 |

| Figure 4-5.  | Tape Transport Interconnect Cabling           | 4-17 |

| Figure 4-6.  | TC03 Formatted/Streaming Combination          |      |

|              | Subsystem                                     | 4-21 |

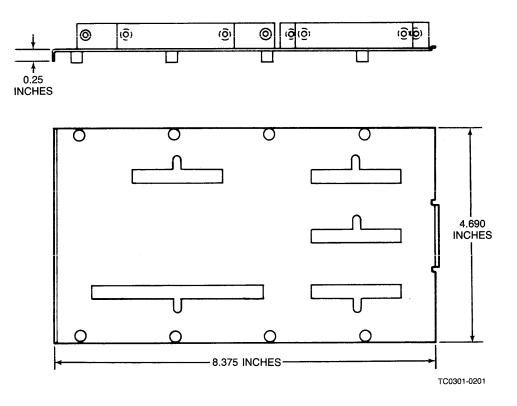

| Figure 4-7.  | CU2220301 Bulkhead Distribution Panel         | 4-23 |

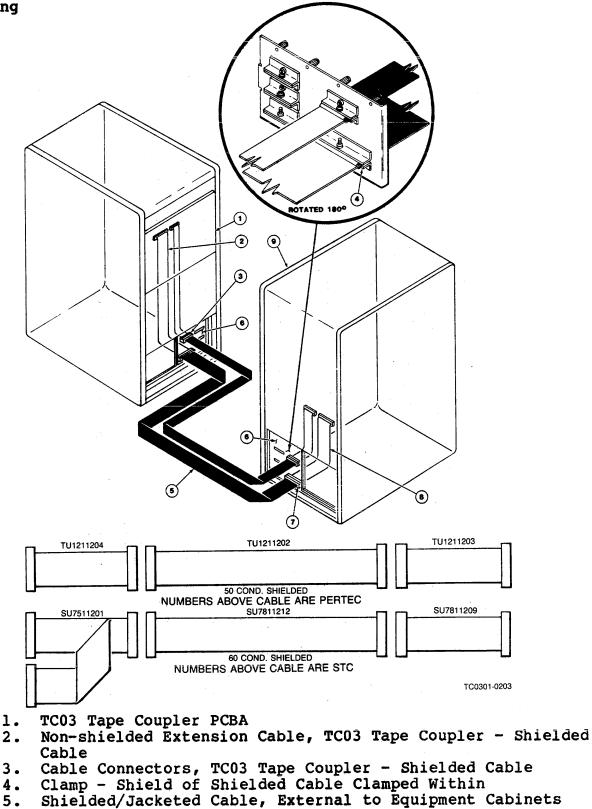

| Figure 4-8.  | RFI-Suppression Cable Installation            | 4-25 |

| Figure 4-9.  | Personality Panel Dimensions                  | 4-27 |

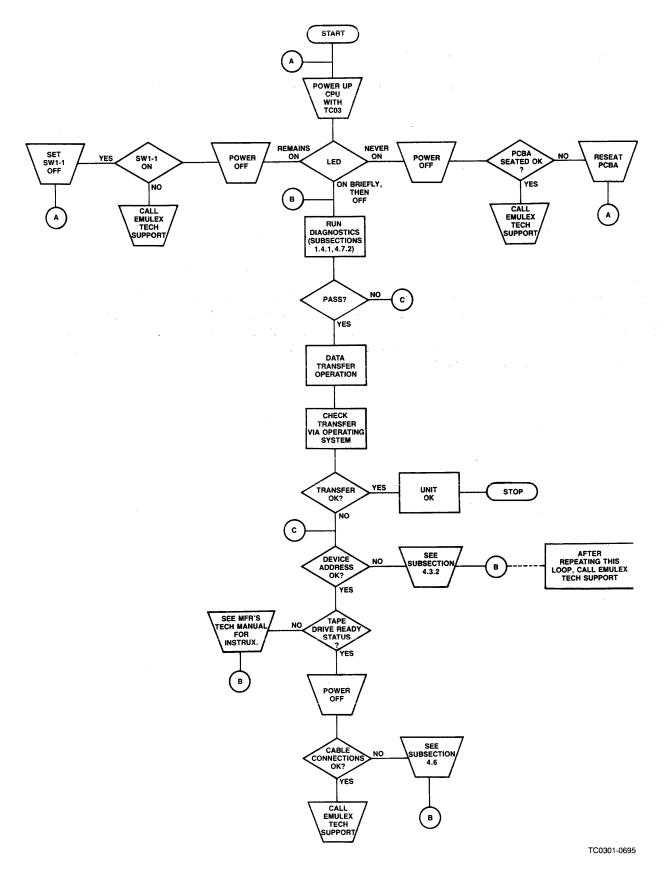

| Figure 5-1.  | Fault Isolation Flowchart                     | 5-3  |

| Figure 6-1.  | TC03 Tape Coupler Registers                   | 6-2  |

| Figure 6-2.  | Byte Swap Sequence, Forward                   | 6-25 |

| Figure 6-3.  | Byte Swap Sequence, Reverse                   | 6-25 |

| Figure 6-4.  | Get Status Command Packet                     | 6-26 |

| Figure 6-5.  | Read Command Packet                           | 6-27 |

| Figure 6-6.  | Set Characteristics Command Packet and        |      |

|              | Characteristics Data Format                   | 6-30 |

| Figure 6-7.  | Write Command Packet                          | 6-32 |

| Figure 6-8.  | Position Command Packet                       | 6-33 |

| Figure 6-9.  | Format Command Packet                         | 6-35 |

| Figure 6-10. |                                               | 6-36 |

| Figure 6-11. |                                               | 6-37 |

| Figure 6-12. | Message Packet Header Word                    | 6-37 |

| Figure 6-13. |                                               | 6-39 |

| Figure 7-1.  | TC03 Tape Coupler Block Diagram               | 7-2  |

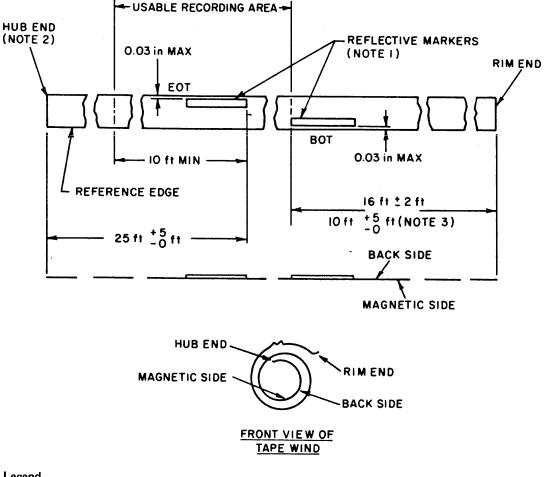

| Figure 7-2.  | Usable Recording Area in 800 cpi NRZI Format. | 7-4  |

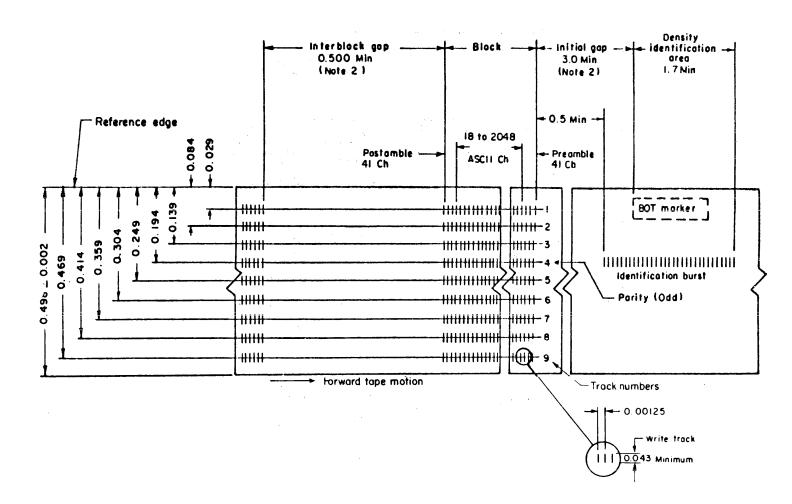

| Figure 7-3.  | NRZI Recording Format                         | 7-5  |

| Figure 7-4.  | Usable Recording Area in 1600 cpi PE Format   | 7-6  |

| Figure 7-5.  | PE Recording Format                           | 7-7  |

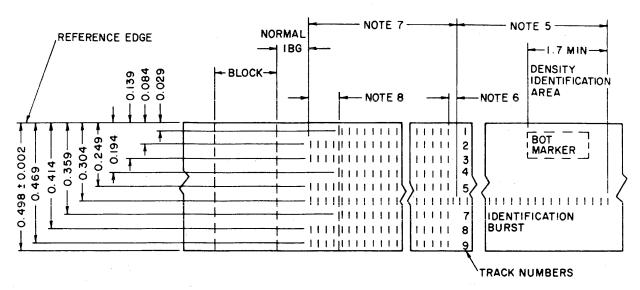

| Figure 7-6.  | Usable Recording Area in 6250 cpi GCR Format. | 7-8  |

| Figure 7-7.  | GCR Recording Format                          | 7-9  |

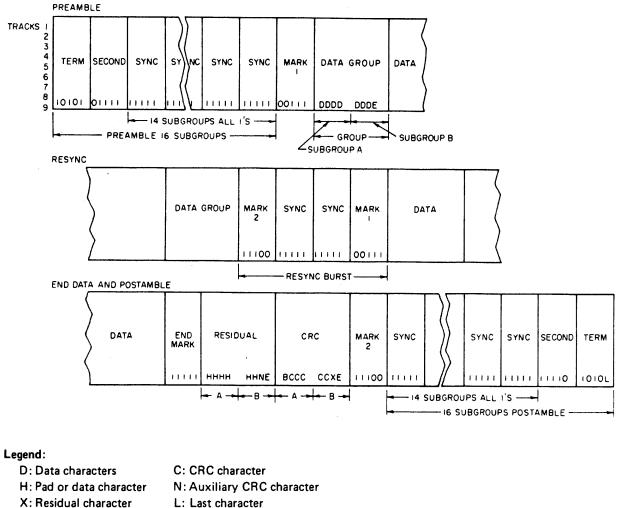

| Figure 7-8.  | Group Organization of GCR Recording Format    | 7-10 |

# LIST OF TABLES

| Table | 1-1. | Basic Subsystem Contents                     | 1-5  |

|-------|------|----------------------------------------------|------|

| Table | 1-2. | Subsystem Options                            | 1-5  |

| Table | 2-1. | TC03 Tape Coupler Specifications             |      |

| Table | 4-1. | TC03 Switch Definitions and Factory          |      |

|       |      | Configuration                                | 4-6  |

| Table | 4-2. | Jumper Definitions                           | 4-7  |

| Table | 4-3. | Tape Coupler Modes                           | 4-7  |

| Table | 4-4. | Transport Addresses in Combination Mode      | 4-8  |

| Table | 4-5. | LSI-11 Bus Starting Addresses                | 4-9  |

| Table | 4-6. | Unshielded Cables                            | 4-18 |

| Table |      | TC03 Coupler to Formatter Connections        | 4-19 |

| Table | 4-8. | Shielded Cables and Installation Hardware    | 4-26 |

| Table |      | Flowchart Symbol Definitions                 | 5-2  |

| Table | 6-1. | Termination Class Codes                      | 6-6  |

| Table | 6-2. | TS11 Bootstrap Routine                       | 6-10 |

| Table | 6-3. | Event Sequences in Buffer Ownership Transfer | 6-17 |

| Table | 6-4. | Command Code and Command Mode Field          |      |

|       |      | Definitions                                  | 6-22 |

| Table |      | LSI-11 Bus Interface Pin Assignments         | 8-3  |

| Table |      | Cable Interface                              | 8-9  |

| Table |      | SYSGEN Device Table                          | A-1  |

| Table | A-2. | Priority Ranking for Floating Interrupt      |      |

|       |      | Vector Addresses (starting at 3008 and       |      |

|       |      | proceeding upward to 7778)                   | A-3  |

| Table |      | Base and Vector Address Example              | A-5  |

| Table |      | Floating Address Computation                 | A-5  |

| Table | B-1. | PROM Locations                               | B-1  |

|       |      |                                              |      |

#### EMULEX PRODUCT WARRANTY

SUBSYSTEM WARRANTY: Emulex warrants all packaged subsystems and their major elements, including host adapters, to be free of defects in material and workmanship for a period of six (6) months following shipment to the customer. In the event of difficulty, the customer should return the questionable assembly to Emulex, freight prepaid. Emulex, at its option, will either repair or replace the unit following confirmation that it is covered by our warranty. Major assemblies are defined as power supply, disk drive, tape drive, and all associated controller circuit boards which make up the packaged subsystem.

SOFTWARE WARRANTY: Emulex warrants for a period of ninety (90) days, either from the date of installation or thirty (30) days after shipment, whichever comes first, that each software package supplied shall be free from defects and shall operate according to Emulex specifications under those Digital Equipment Corporation ("DEC"), IBM, Intel, and Unix operating system versions supported by Emulex. Emulex does not warrant its software products under any operating system that has not been specifically identified. Any software revisions required hereunder will cover supply of distribution media only and will not cover on-site installation of integration.

MEDIA WARRANTY: (Return to Factory) - Media not covered by on-site warranty is warranted for thirty (30) days from date of shipment. The customer is responsible for return of media to Emulex and Emulex for freight associated with replacement media being returned to the customer.

GENERAL TERMS: The above warranties shall not apply to expendable components such as fuses, bulbs, and the like, nor to connectors and other items not a part of the basic product. Emulex shall have no obligation to make repairs or to cause replacement required through normal wear and tear or necessitated in whole or in part by catastrophe, fault or negligence of the user, improper or unauthorized use of the Product, or use of the Product in such a manner for which it was not designed, or by causes external to the Product, such as, but not limited to, power failure or air conditioning, Emulex's sole obligation hereunder shall be to repair or replace items covered in the above warranties. Purchaser shall provide for removal of the defective Product, shipping charges for return to Emulex, and installation of its replacement.

RETURNED MATERIAL: Warranty claims must be received by Emulex within the applicable warranty period. A replaced product, or part thereof, shall become the property of Emulex and shall be returned to Emulex at Purchaser's expense. All returned material must be accompanied by a RETURN AUTHORIZATION number assigned by Emulex. INSTALLATION/ON-SITE SERVICE WARRANTY: For the customer who prefers repair of his equipment on-site, Emulex offers installation with an included ninety (90) days on-site maintenance service. Under this plan, the Emulex subsystem is installed and fully checked out by Emulex authorized representatives. Following installation, all reported problems are corrected at the customer facility. All elements of the system, including cables, Emulex supplied media, etc., are covered by this service. This provides the customer with maximum availability of the equipment in the event of a problem and precludes the necessity of returning defective parts to the factory for repair under the standard return to factory warranty.

#### NOTE

All expressed and implied warranties concerning the subsystem portion of this warranty are considered null and void if the subsystem is operated in a partially disassembled state. The subsystem must be run with all covers and outer shells in place.

THE EXPRESSED WARRANTIES SET FORTH IN THIS AGREEMENT ARE IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING WITHOUT LIMITATION, ANY WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, AND ALL OTHER WARRANTIES ARE HEREBY DISCLAIMED AND EXCLUDED BY EMULEX. THE STATED EXPRESSED WARRANTIES ARE IN LIEU OF ALL OBLIGATIONS OR LIABILITIES ON THE PART OF EMULEX FOR DAMAGES, INCLUDING BUT NOT LIMITED TO SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES ARISING OUT OF, OR IN CONNECTION WITH THE USE OR PERFORMANCE OF THE PRODUCT.

## Section l GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

This manual provides information related to the capabilities, design, installation, and use of the TCO3 Magnetic Tape Coupler manufactured by Emulex Corporation.

The manual contains eight sections and two appendices:

- Section 1 General Description. This section contains an overview of the TCO3 Magnetic Tape Coupler.

- Section 2 **Specifications.** This section contains specification tables for the TC03.

- Section 3 **Planning the Installation.** This section contains the information necessary to plan your installation.

- Section 4 Installation. This section contains the information necessary to set up and physically install the TC03.

- Section 5 **Troubleshooting.** This section describes preventive maintenance and fault isolation procedures for maintaining optimum performance of the TCO3.

- Section 6 **Coupler Registers and Programming.** This section describes the registers and command packets.

- Section 7 Functional Description. This section describes TC03 architecture.

- Section 8 Interfaces. This section describes the tape transport interface and LSI-11 bus interface.

- Appendix A **Autoconfigure, Base and Vector Addresses.** This appendix explains use of the algorithms for assignment of floating addresses and floating interrupt vector addresses used with RSTS/E and RSX-11M devices.

- Appendix B **PROM Removal and Replacement.** This appendix provides instructions for removing and replacing PROMs.

- Appendix C **Drive Configurations.** Presents configuration instructions for supported tape drives.

# 1.1.1 RELATED DOCUMENTATION

The DEC manuals listed in this subsection may be ordered from the following address: Digital Equipment Corporation P.O. Box CS2008 Nashua, NH 03061 Title: RSX-11M System Generation and Installation Guide Publication Number: AA-H625C-TC Title: RSX-11M-PLUS System Generation and Management Guide Publication Number: AA-H431A-TC Title: RT-11 Software Support Manual Publication Number: AA-H379B-TC Title: RSTS/E System Generation Manual Publication Number: AA-2669G-TC Title: MicroVMS User's Manual Publication Number: AA-Z209B-TE

The following DEC publication may also be useful to readers:

The DEC Dictionary: A Guide to Digital's Technical Terminology

Available from:

Digital Press 30 North Ave. Burlington, MA 01803

# 1.1.2 DEFINITIONS OF TERMS

This manual uses standard DEC terminology wherever possible. For definitions, see the DEC Dictionary (referenced in subsection 1.1.1). In some cases, however, Emulex has adopted alternate conventions in order to avoid the use of potentially ambiguous terms. Possible exceptions to standard usage are defined in this subsection.

- As applied to tape transports, the terms non-streaming, formatted, and start/stop are used interchangeably in this document.

- The term LSI-11 bus, as used in this document, is synonymous with DEC's Q-Bus.

- The term base address represents the same concept as the commonly-used terms LSI-11 bus address, CSR address, and device address. Because the TC03 has no Control and Status Register per se, the expression "CSR address" is avoided in this document wherever possible. In DEC prompts (e.g., subsection 4.7.2), "CSR" refers to the TSSR (Status Register), which is located at the base address plus 2.

- The term **file mark**, as used in this manual, is synonymous with **tape mark**.

- The term **subsystem**, as applied to the TC03, refers to an individual emulation (the tape coupler plus one transport). As explained in subsection 1.2, the TC03 emulates four DEC TS11 subsystems.

#### **1.2 SUBSYSTEM OVERVIEW**

The TC03 is an intelligent, microprocessor-based tape coupler that is capable of connecting up to four tape transports to DEC computer systems that use the LSI-11 bus. The tape transports must have internal formatters that use the industry-standard Pertec interface.

When used with an appropriate formatter and tape transports, the TCO3 performs a software transparent emulation of four DEC (Digital Equipment Corporation) TS11 Tape Subsystems. The TCO3 is supported by all DEC operating systems that run on LSI-11 systems (not including MicroVMS). The TCO3 also supports the bootstrap options of DEC's TK25 and TSV05 Tape Subsystems. The TCO3 is compatible with the standard TSDRIVER software supplied in DEC operating systems.

The TC03 functions with both streaming and non-streaming tape transports with integral formatters. The operating mode is determined by means of switches on the operator control panel of the tape transport, as explained in Section 4 of this document. The TC03 is hardware compatible with non-streaming (formatted) nine-track tape transport systems that operate with any of the following formats:

- Non-Return to Zero Inverted (NRZI) format at 800 bits per inch (bpi)

- Phase Encoded (PE) format at 1600 or 3200 bpi

- Group Code Recording (GCR) format at 6250 bpi

- Dual density (NRZI/PE or PE/GCR)

- Tri-density (NRZI/PE/GCR)

Streaming tape transports operate with the following formats:

- PE

- GCR

- Dual density (PE/GCR)

System tape transports may operate at any of the industry standard tape speeds from 12.5 to 140 inches per second (ips). In nonstreaming mode, typical tape speed is 25 ips; check the manufacturer's specification for the exact speed. In streaming mode, typical tape speed is 100 ips. The TCO3 shifts from non-streaming to streaming mode automatically if enough data is available to support the higher throughput rate. The shift is software transparent.

Tape transports supported by the TCO3 may have any combination of formats and tape speeds within the range defined above.

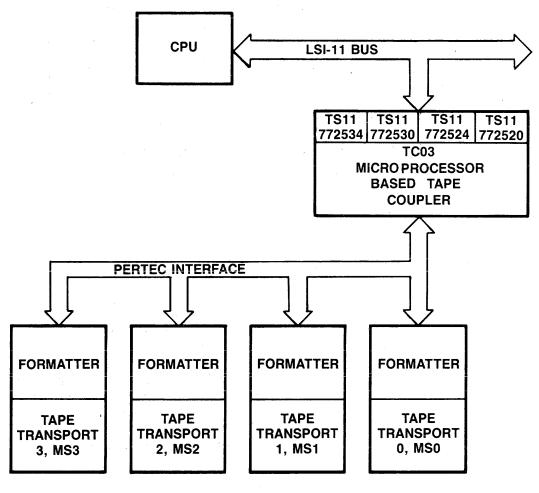

Figures 1-1 and 3-2 show two possible TC03 subsystem configurations.

TC0301-0691

#### **1.3 PHYSICAL CHARACTERISTICS**

The TCO3 is a microprocessor-based emulating tape coupler, located on a single quad-size, four-layer printed circuit board assembly (PCBA). The PCBA plugs directly into any LSI-ll bus slot and into connectors A, B, C, and D of the backplane, from which it draws its power. Two 50-wire flat cables connect the TCO3 to the embedded formatter in the first tape transport.

# 1.4 SUBSYSTEM MODELS AND OPTIONS

The TC03 Tape Coupler is pictured in Figure 1-2. A single model of the TC03 is offered: the TC03. The TC03 is identified by a toplevel assembly tag that is glued to one of the 2901 bit-slice microprocessor chips on the PWB. The TCO3 top level assembly number is given in Table 1-1, along with the part numbers of the items that are delivered with the TCO3.

| Item | Qty | Description           | Part Number   | Comment                      |

|------|-----|-----------------------|---------------|------------------------------|

| 1    | 1   | TC03 Tape Coupler     | TC0310201-FSX | X is<br>firmware<br>revision |

| 2    | 1   | TC03 Technical Manual | TC0351001     | 160181011                    |

| 3    | 1   | 22-Bit Addressing Kit | CS0113001     |                              |

# 1.4.1 SUBSYSTEM OPTIONS

Table 1-2 lists the options that can be ordered to tailor your TCO3 to your particular application.

| Option       | Description                                                                                                                                                                                    |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD9951802-01 | Backup and Restore Program (BRP).<br>Allows image backup and restoration of<br>disk. Compatible with the following<br>disk/tape subsystems and all Emulex<br>emulations of these DEC products: |

|              | TS11<br>RK06/07<br>RL01/02<br>RM02/03/05/80<br>RP06<br>UDA50                                                                                                                                   |

|              | Distributed on 0.5-inch tape, PE format<br>with MS boot. Not available for<br>MicroVAX.                                                                                                        |

Table 1-2. Subsystem Options

(Continued)

| VD9960703 | MicroVMS TSll Software Driver<br>(TSDRIVER). This optional Emulex<br>software driver makes your TC03<br>compatible with MicroVMS (MicroVAX I and<br>II). Distributed on 5.25-inch diskette. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VX9960704 | MicroVAX TSll Emulation Installation<br>Diagnostic (IQTl2). An installation<br>diagnostic for Emulex TCO3 and QTl2 tape<br>couplers; distributed on 5.25-inch<br>diskette.                  |

Table 1-2. Subsystem Options (Continued)

Options are specified as separate line items on a sales order. An example of a sales order is shown in Figure 1-3.

| Item | Model Number | Comment/Description        |

|------|--------------|----------------------------|

| 1.   | тсоз         | TC03 Tape Coupler          |

| 2.   | PD9951802-01 | Backup and Restore Program |

# Figure 1-3. Sales Order Example

TC0301-0692

Figure 1-2. TC03 Tape Coupler

## 1.5 FEATURES

The TC03 Tape Coupler design incorporates several features that enhance performance.

#### 1.5.1 MICROPROCESSOR ARCHITECTURE

The TC03 Tape Coupler circuitry incorporates an eight-bit, high-speed bipolar microprocessor with AMD 2901-type bit-slice components. The microprocessor design approach provides a reduced component count, high reliability, easy maintainability, and the means to adapt a single set of hardware to a wide range of emulation capabilities through the use of microprogramming.

# 1.5.2 CONFIGURATION FLEXIBILITY

Configuration flexibility is provided by three DIP switch packs on the PCBA, which are used for configuring the operating characteristics of the TCO3 Tape Coupler. These characteristics include device and interrupt vector address selection and other options.

#### 1.5.3 SELF-TEST

The TC03 Tape Coupler firmware incorporates an internal self-test routine that is executed every time the computer/tape transport system is powered up. This test exercises all parts of the microprocessor, buffer, and data-handling logic. This self-test does not completely test all circuitry in the TC03, but successful completion indicates a high probability that all circuits are operational.

#### 1.5.4 BUFFERING

The TC03 Tape Coupler includes 3.5K bytes of data buffering. It transfers to or from memory on a word basis, except for odd bytes at the start or end of the record. This feature enables the TC03 to support high-speed GCR transports.

#### 1.5.5 DATA TRANSFER

The TCO3 supports DMA (direct memory access) data transfers in 16-, 18-, or 22-bit addressing mode, or block mode transfers with an adaptive DMA algorithm. LSI-11 bus DMA speed is up to 2M bytes per second, or 3.5M bytes in block mode.

#### 1.5.6 BOOTSTRAP OPTIONS

The TC03 supports three bootstrap options: DEC TSV05 and TK25, the Emulex bootstrap option, and the standard DEC TS11 bootstrap. The Emulex bootstrap option is a bootstrap hand-load routine that makes it possible to bootstrap easily if your system lacks a boot PROM that supports the TC03.

#### **1.6 COMPATIBILITY**

# 1.6.1 MEDIA COMPATIBILITY

Tapes written according to ANSI Standard X3.40-1976 are interchangeable with tapes written by tape transports with the TC03 Tape Coupler.

## **1.6.2 TAPE TRANSPORTS**

The TCO3 Tape Coupler is compatible with nine-track tape transports that can be operated in formatted mode (Pertec interface) or streaming mode (modified Pertec interface), at data densities of 800 bpi (NRZI), 1600 bpi (PE), or 6250 bpi (GCR), and at all standard tape speeds from 12.5 to 140 ips. The following transports are supported:

- Kennedy 9220 formatter with attached 9000, 9100, and 9300 drives

- Kennedy 9400 embedded formatter drives

- CDC 92181, 92185, and 92185-02

- Cipher 891 and 990

Although most of the signals in the Pertec interface are well standardized, a few of them are interpreted differently by individual tape drive vendors. The TCO3 option switches are used to accommodate these differences, as explained in Section 4 of this document.

#### NOTE

Non-buffered CDC 92185 tape transports can be operated at 1600 bpi (PE) only.

# 1.6.3 DIAGNOSTICS

The TC03 Tape Coupler executes the following DEC TS11 PDP-11 diagnostics in NRZI, PE, and GCR modes:

ZTSH - Data Reliability

ZTSI - Coupler Repair Diagnostic (runs first three tests)

For a list and description of available Emulex TCO3 diagnostics, see Table 1-2.

#### 1.6.4 OPERATING SYSTEMS

The TC03 Tape Coupler is fully compatible with the TS Driver software used with the following DEC operating systems:

RSTS/E RSX-11M RSX-11M PLUS RT-11 MicroVMS (see also subsection 1.4, Options)